Selective Area Growth

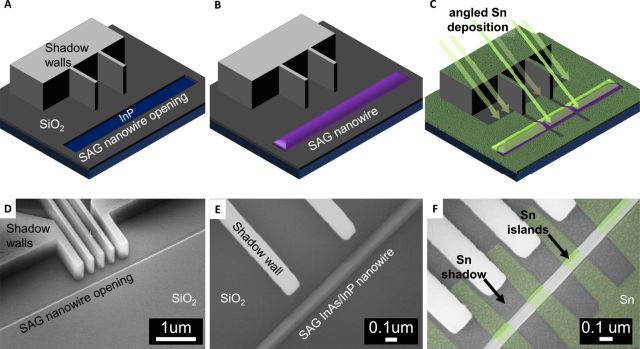

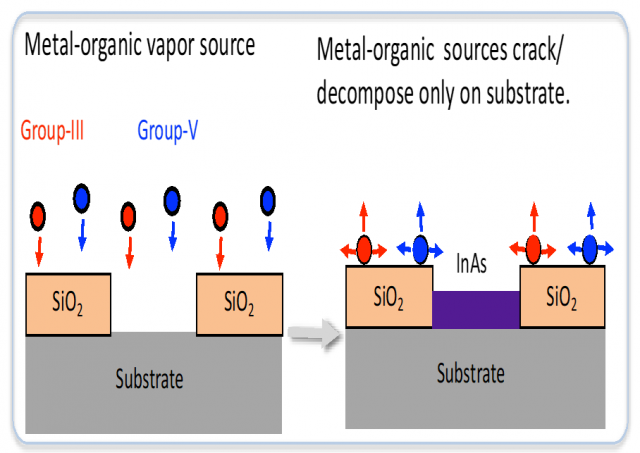

We grow in-plane semiconductor nanowires as scalable platforms for quantum information processing. By depositing a superconductor onto these selectively grown nanowires, we can induce topological superconducting phases capable of hosting Majorana zero modes. Our group develops superconductor–nanowire hybrid systems using Selective Area Growth (SAG) techniques, with the goal of scaling nanowire networks for use in topological qubits and ultimately building a fault-tolerant quantum computer.

SAG also enables lateral growth of III–V epitaxial films for next-generation semiconductor devices. Using pre-patterned dielectric templates to control nucleation and lateral growth direction—an approach known as Confined Epitaxial Lateral Overgrowth (CELO)—we achieve precise control over fin geometries and composition. This technique supports the fabrication of low-power, high-on-current Tunnel Field-Effect Transistors (Tunnel FETs), lateral heterojunctions for advanced device concepts, photonic virtual substrates, and monolithic III–V integration on silicon.